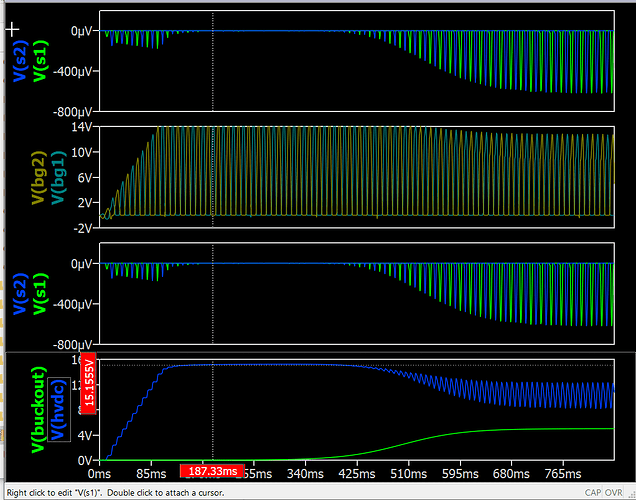

The circuit being simulated is an AC-to-DC subsystem comprised of: 1) AC source with Rs, 2) bridge rectifier (with 2 NMOS FETs as synchronous rectifiers to improve efficiency) 3) bulk filter cap, and 4) macro model for a buck converter, and 5) a constant power current source for load. I am operating on the “low power” side of MPP, which should be stable. Anyway, the transient waveform shows no sign of instability. It appears to have reached steady state, and then BAM! Fatal error occurs.

It truly seems to be an issue with QSPICE’s solver, as opposed to a circuit issue.

Upload you schematic to let us review what can be done. Timestep is too small is common in Spice simulation and not necessary relate to stability but more about I-V is too steep. Or search this forum, we post general direction in resolve timestep too small issue.

Thing to try include

- use 80 bits math solver with this directive

.option fastmath=0.

- limit maximum timestep with directive

.option maxstep=<value>. Sometime you need a smaller timestep to help convengence.

- change trtol for timestep control. It is hard to say set it loose or tighten can help.

.option trtol=<value>.

- increase transient iteration limit with

.option itl4=<value>

- change integration methed, try gear insteat of trap with directive

.option method=gear

Other method include gshunt, cshunt, reltol, smooth switch with negative Vh etc…

Don’t be surprise by timestep is too small error, everyone plays with SPICE-based simulator and experience that.

Parent.Super_Bridge.qsch (18.7 KB)

SL_1W_3Wpeak_PowerWave.txt (2.2 MB)

Super_Bridge.qsch (16.4 KB)

BSS84.qsym (1.4 KB)

BSS123.qsym (1.4 KB)

LM74680.qsym (622 Bytes)

NMOS.qsym (1.3 KB)

PMOS_SOT23.qsym (1.3 KB)

diode.txt (1.2 KB)

mos.txt (3.1 KB)

Hello KS Kelvin - my references assume that the .qsym files are in a folder called “symbols” and the diode.txt and mos.txt are in a folder called “models”.

I pulled my hair out trying to get rid of this “Timestep too small error.” I think I tried everything, but maybe you have the right experience to crack this nut. The circuit is basically a high efficiency bridge rectifier with NMOSFETs, driven by a transformer. Load is applied later in time. An additional load is applied at 0.5sec, which is a noisy PWL file, with time steps of 1msec.

Thank you in advance if you get a chance to look at this.

Cheers!

LM74680.qsch is missing.

Did your circuit work before implementing that complex loading?

LM74680.qsch (34.3 KB)

Hello KSKelvin,

My apologies for the omission.

Did it run without crashing without the complex load? Sometimes yes, sometimes no. I’ve had the circuit run fine without a noisy file, and I’ve also had it “crash” due to time step too small, even with a constant dc load. By the way, I verified the noisy load waveform (which represents power, but uses voltage as a proxy) has average value of 1W and peak power of 3W. The file has values every 1msec, which limits the slew rate to a reasonable value.

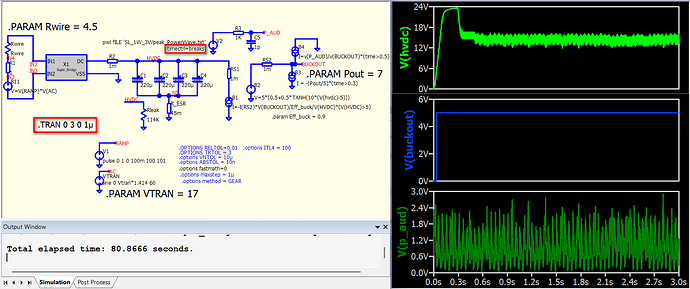

Firstly, there are two minor mistakes in your schematic:

- You have a typo in

.options method=gear; therefore, Qspice warns you about that.

- The

.tran syntax is incorrect for Traditional Berkeley Syntax. Go to Qspice help to take a look. This example is correct version; store data from 0s to 3s, with a maxstep of 1us. You have made the right move, as setting a maxstep is necessary to help this circuit converge.

The essential change that resolves the timestep being too small in this case is to add an attribute timectrl=breaks to your PWL source V2. This can force the simulation timestep to hit each breakpoint in the data. Without that, Qspice may interpolate data from the PWL data. It seems the timestep being too small is related to allowing such an operation; that’s why the solution is to force an exact timestep at each breakpoint.

(remark : In my Qspice device guideline, goto V-source section, a slide explains what timectrl behave for a PWL V-source, currently is about p.243)

This simulation can run with fastmath enabled or disabled. As this circuit seems complex, I have left fastmath disabled. Other options do not seem necessary. Hope this help.

Parent.Super_Bridge-ResolveTimeStepTooSmall.qsch (18.7 KB)

1 Like

There is another option that can help this schematic to converge if you are not using timectrl=breaks for V2.

Add .option trtol=1; Qspice defaults trtol=2.5. Instead of increasing that value, sometimes reducing this value can help. TRTOL controls how the timestep responds; my understanding is that a larger value results in a rougher timestep.

1 Like