Can you explain why SiC FETs have a lower Rdson?

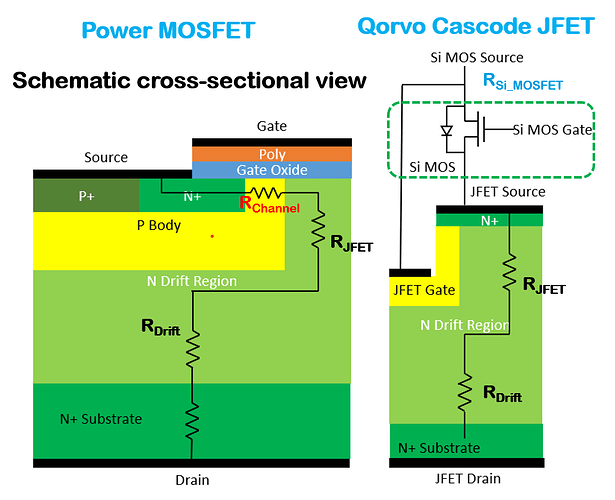

This is because Cascode structure combines low-voltage Si MOSFET and high-voltage SiC JFET. For low-voltage Si MOSFET, the on-resistance is low; for high-voltage SiC JFET, because it does not have the R-Channel comparing to normal power MOSFET, the on-resistance is also low. Besides, SiC JFET dominates the chip size and the total Rdson, so for a given chip size, SiC FETs have a lower total Rdson, comparing to normal power MOSFET.

1 Like