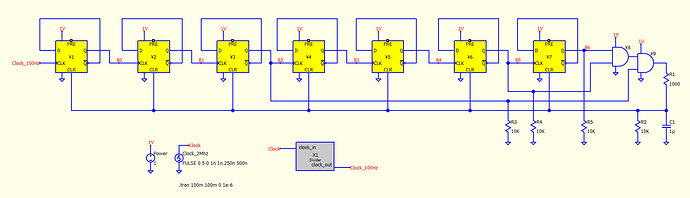

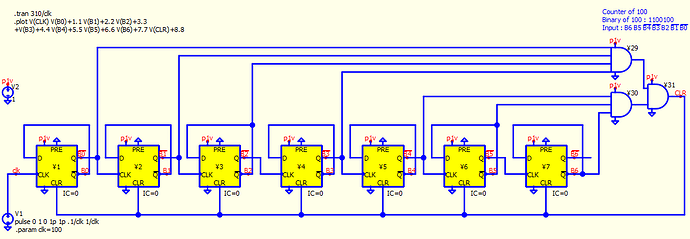

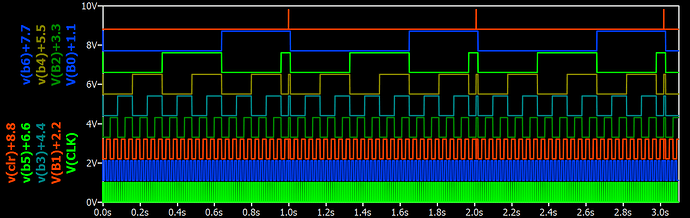

I am creating a simple binary up counter with reset when decimal 100 comes in the output and circuit is as below.

The Block is a verilog code for divide by n logic for converting 2Mhz to 100hz.

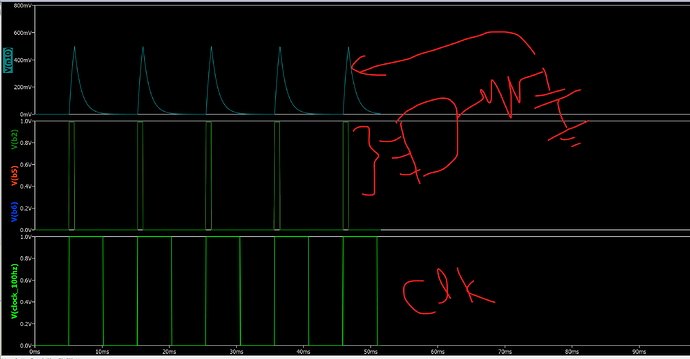

RC circuits are added to clear out the spikes, but also not solving the issue.

Below is the snippet of clock input, input and output of AND gate.

Why this is happening? Where am doing wrong in this case?