Hi Mike,

I am running a co-sim with QSPICE and verilator model with timing.

My Trunc function is set-up to force the simulator to hit the exact timeslots required by the verilator model. If the incoming t is greater than the next verilator timeslot then I set *timestep to the required dt based on the t from the last evaluation. Here’s a code snippet.

if (((uint64_t)(t * 1e12)) > (vinst->nextTimeSlot()))

{

*timestep = vinst->nextTimeSlot() * 1e-12 - (opaque)->t_last;

printf(“>trunc_t = %f: * Shortening timestep: from dt = %f to %f, new t = %f\n”, t * 1e9, timestep_in *1e9, *timestep * 1e9, ((opaque)->t_last + *timestep ) * 1e9);

}

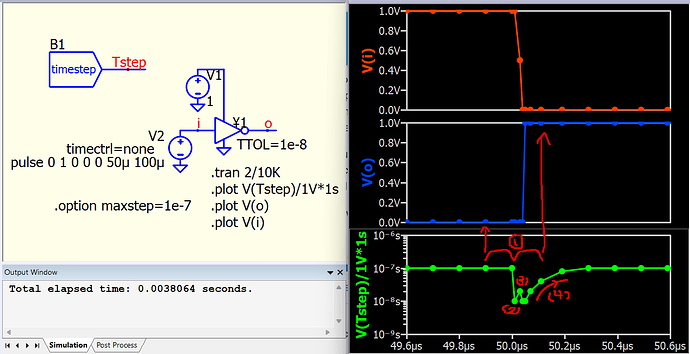

This runs fine for about 2.6ms of simulation time but then, for no apparent reason, the simulator ignores the *timestep that I requested.

See debug output below for a few timesteps upto and including the bug…

1st number is the proposed t coming into trunc()

2nd number is proposed t minus the last t evaluated.

3rd number is my *timestep requested

4th number is my calculated next evaluation time.

trunc_t = 261255.000000: * Shortening timestep: from dt = 10.000000 to 5.000000, new t = 261250.000000

trunc_t = 261300.000000: * Shortening timestep: from dt = 10.000000 to 5.000000, new t = 261295.000000

trunc_t = 261305.000000: * Shortening timestep: from dt = 10.000000 to 5.000000, new t = 261300.000000

trunc_t = 261350.000000: * Shortening timestep: from dt = 10.000000 to 5.000000, new t = 261345.000000

trunc_t = 261355.000000: * Shortening timestep: from dt = 10.000000 to 5.000000, new t = 261350.000000

trunc_t = 261366.376635: * Shortening timestep: from dt = 9.448432 to 3.071797, new t = 261360.000000

trunc_t = 261375.104877: * Shortening timestep: from dt = 10.000000 to 4.895123, new t = 261370.000000

trunc_t = 261375.181704: * Shortening timestep: from dt = 5.984263 to 0.802559, new t = 261370.000000

trunc_t = 261388.468266: * Shortening timestep: from dt = 9.101943 to 0.633677, new t = 261380.000000

trunc_t = 261398.871480: * Shortening timestep: from dt = 10.000000 to 1.128520, new t = 261390.000000

trunc_t = 261396.771123: * Shortening timestep: from dt = 4.514082 to 2.742959, new t = 261395.000000

trunc_t = 261400.485918: * Shortening timestep: from dt = 5.485918 to 5.000000, new t = 261400.000000

-V{t1,1}@261400.486000: missed 261400.000000

%Error: C:\Users\datkin\source\repos\verilator\install\include\verilated_timing.cpp:84: %Error: Encountered process that should’ve been resumed at an earlier simulation time. Missed a time slot?

There are no other trunc() functions active in the sim

Near the bug the analog simulator is reducing timesteps to follow a falling edge. I would expect the simulator to always respect the min *timestep that is requested by trunc. Is this a reasonable expectation?

With thanks

Dale