The problem you encountered, I am no expert but just to share what I observe or know (could be wrong)

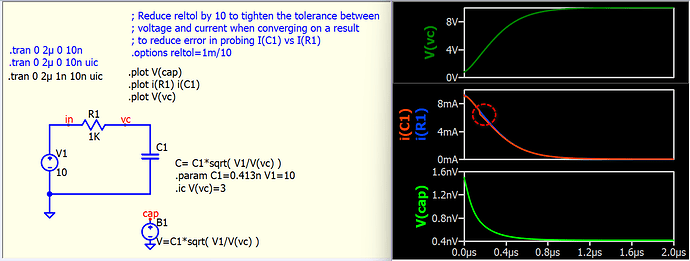

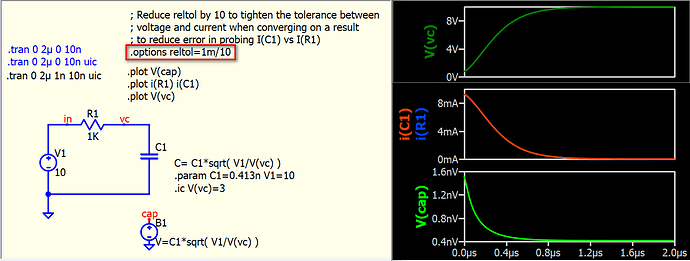

Difference between current through the resistor and capacitor

Sometime, you can see difference in current for devices connected in series in SPICE simulation. SPICE uses Modified Nodal Analysis (MNA) to solve the circuit. My understanding is that, SPICE arranges circuit into a matrix with conductance * voltage = current (i.e. [G][V]=[I]) and use Newton-Raphson Method to solve for the voltage. Then it verify if sum of current into a node is within certain tolerance (reltol, abstol) as one of the convergence criteria.

Not sure how changing capacitance plays a part of it, but currently relative tolerance is too loose and simulator accepted this as a solution. Well, never be too surprise in seeing weird current as this is how spice works. Here are two discussion I recall, about weird current during simulation

https://forum.qorvo.com/t/current-imbalance-with-behavioural-sources/19312/7

https://forum.qorvo.com/t/persistent-bug-warning-singular-matrix-check-node-b/17636/22

I think @frank.wiedmann and @OHara have better understanding in this topic than mine.

Here, is a comparison by reducing reltol by 10 times for same setup

2.- Non-linear-cap-qspice (retol).qsch (3.7 KB)