Hi,

I am tying to implement a few Verilog modules and i cant change the default Rout parameter from 1000. And i cant figure out the syntax. Trhis is my minimalist Verilog module code:

// Automatically generated .v file on Mon Aug 4 09:30:41 2025

//

module test1_verilog ( vcc, clk_in, pwm_out ) ;

// You will probably want to flush out the nature of these port declarations:

input real vcc;

input reg clk_in;

output real pwm_out;

// Implement the module here

assign pwm_out = vcc * clk_in;

endmodule

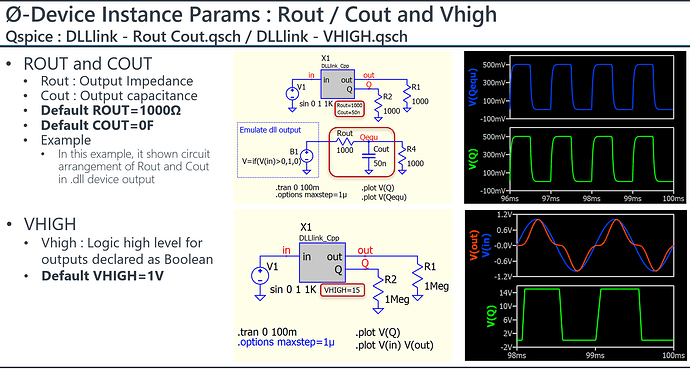

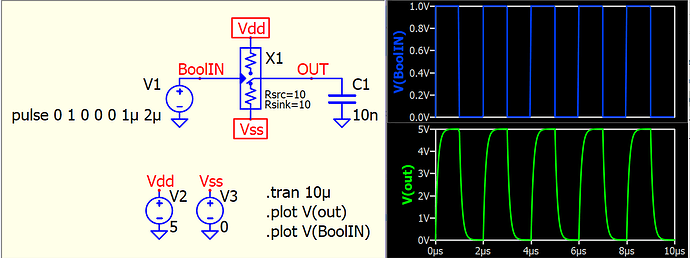

and no matter what i do i cant get Rout parameter to work with my output. I would like to make it low impedance or 50 ohm.

This will become a clock generator + voltage shifter, as of now i see some GND shift for some reason and i suspect the Rout.

Also is this a Thevenin Equivalent circuit?