HI,

So basically I cant get Verilog to output anything besides 0V.

And i cant figure out what i am doing wrong.

Can anyone help me please?

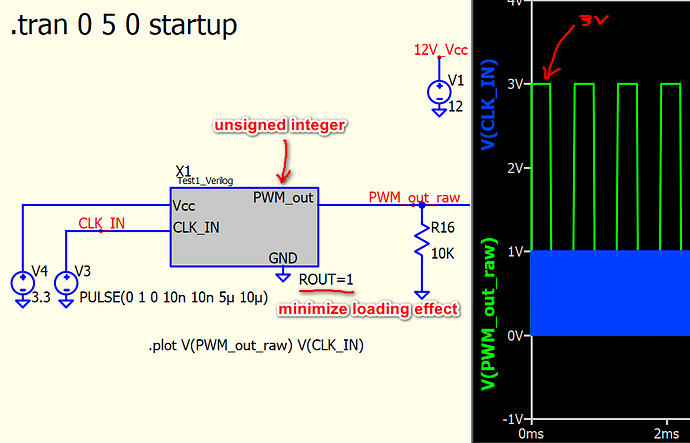

The module is supposed to take a 1MHz clock and Vcc that is the output voltage LVL.

The PWM output signal tries to be a PWM signal from a counter that i implemented inside based on the 1MHz clock. No matter how i modify the module i get only true 0 ot the PWM output.

BTW i am not sure that the Verilog module is embedded in the main file so i am also attaching it here , just to make sure.

test1_verilog.v (870 Bytes)

My_Test.qsch (10.8 KB)

Also overall the simulation tries to be a PWM based DAC.

I am trying to emulate a MCU PWM peripheral where i have a base clock and i can vary the PWM resolution and frequency.

Why did i chose Verilog? Since i plan to do more advanced stuff later on so i started with something relatively basic. And antivisus hates the .DLL files C modules make but that is a problem for another thread/day.

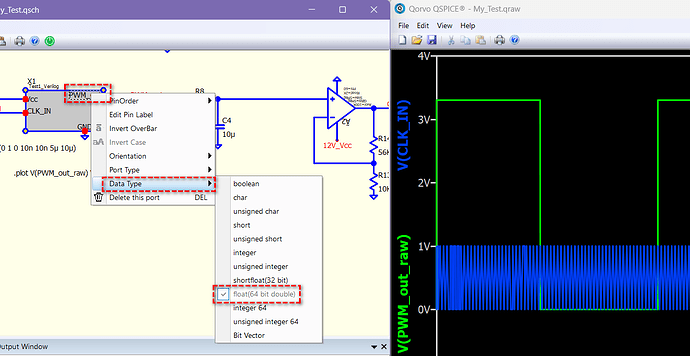

I download your schematic and verilog, and its PWM_out can generate 0V/3V output (as it defined as unsigned integer, it won’t output 3.3V when you set pwm_out = vcc). So, you cannot get 0V/3V output from your uploaded files?

Interesting, when i run the files locally i get only 0 on the PWM_out.

Ill do the changes you recommended and see what happens.

This is what i get with the changes made:

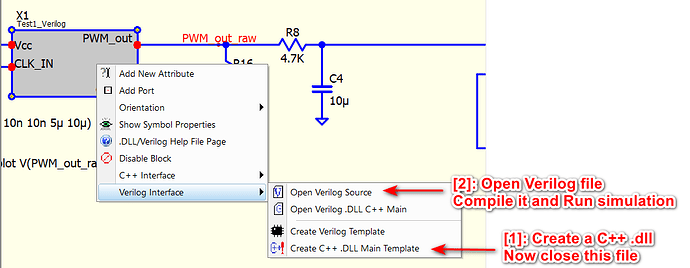

I didn’t change anything (Rout is just to reduce loading effect, without it I can still get ~3V output)… well… is there problem in your compile workflow?

I suggest you delete everything and just have your schematic and verilog file, as like what I download from your post, and follows these two step in picture. You have to create a C++ .dll main template if you modify any pin (add, delete, modify their input/output type or data type)

Moved to another folder:

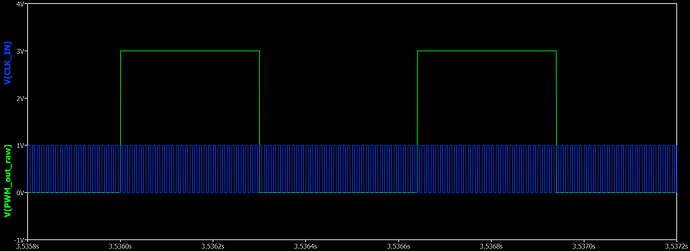

Massive progress!

now i wander can i get to output 3v3 ? anyway 3V is close enough, i can account fot it in the op amp

Change Data Type to “float(64 bit double)”, re-create C++ template. This change don’t need to re-create Verilog Template. Just Re-create C++ .DLL Main Template > Re-compile Verilog file, and you should have output in floating point.

By the way, DLL’s GND is not a necessary pin for DLL-block. If your input and output voltage level are reference to 0 node (circuit GND), you don’t need to add DLL’s GND pin.

In the end it worked but apparently i need to purge all files except the .Qsch and .V files

THX for the help

Hi Robert_1,

I think this issue might be related to the *.cpp file.

Whenever I modify my Verilog code, I delete the *.cpp file and rebuild the project.

That seems to solve the issue.

It looks like the *.cpp file doesn’t get updated when I rebuild after modifying the Verilog code. Even though the *.DLL file is refreshed, the *.cpp file remains unchanged.

I’m not sure if this is the actual cause of the issue, but I’ve found that manually deleting the *.cpp file is necessary whenever I make changes to my Verilog code