Thank you for your response. Yes, I understand now.

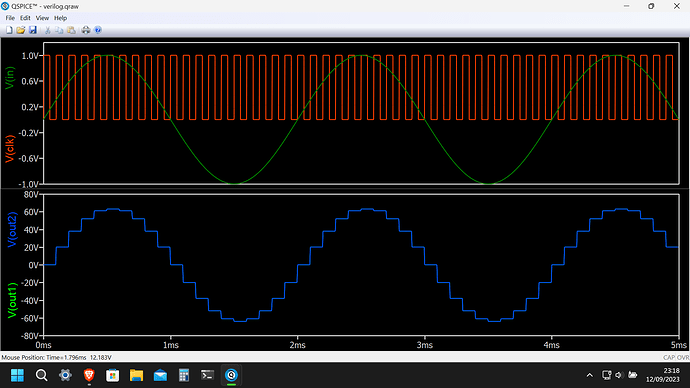

Initially, when using $display("%b\t%d\n", out2, out2), I observed that the representation is preserved. I had concerns that the representation of the numbers from the output (in this case, out2) wouldn’t be maintained outside of Verilog. This concern arose because the waveform viewer did not interpret them as negative, and the C++ DLL generated treated them as unsigned char.

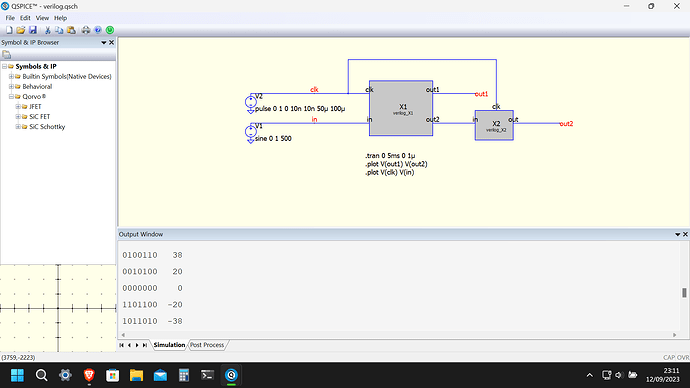

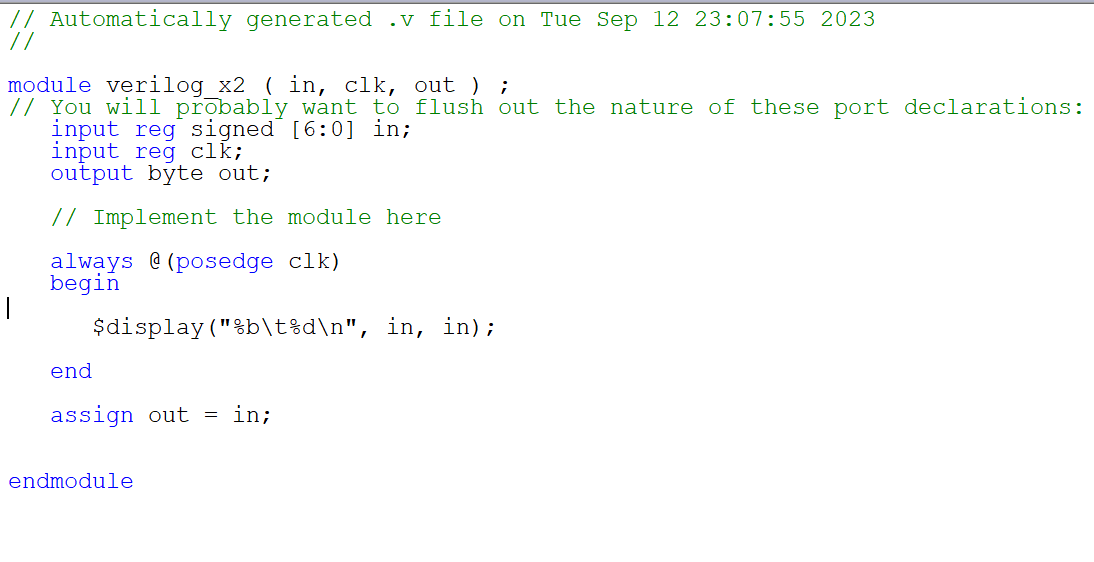

Thanks to your suggestion, I added another Verilog block, and indeed, the representation is preserved (I also included the signed attribute for the input vector):

So, talking to myself: treat those numbers as you want, the next stage will decide if the sequence of bit will be signed or unsigned (I taught that the C++ compiler would make this automatically).

I learnt something new. WOW QSPICE.