I believe @macsky raised a concern that there might be a wrong connection.

Generate pulse for inverter multilevel - QSPICE - Qorvo Tech Forum

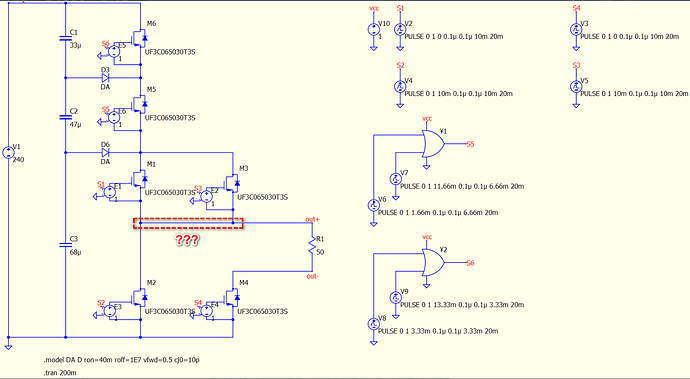

It appears that your idea for the multilevel inverter involves a full-bridge configuration, with the rail voltage controlled by manipulating M5 and M6, to shift the rail and therefore, to shift output voltage level. However, as @bordodynov pointed out, how can this capacitor divider approach operate without discharging throughout the operation?

Moreover, you are driving a FET model rather than an ideal switch, and it seems that your Vgs values are 0V and 1V. How can this voltage level effectively drive the FET model to turn ON and OFF? Your previous version even seems to be better than this one.

Inverter Multilevel - QSPICE - Qorvo Tech Forum

PSIM can work? Have you added a load in PSIM like what you showed in Qspice?

I see multiple posts on this topic, and the clarification seems to have been ignored, leading to the opening of the next post. I’m somewhat losing track of how to provide you with support.