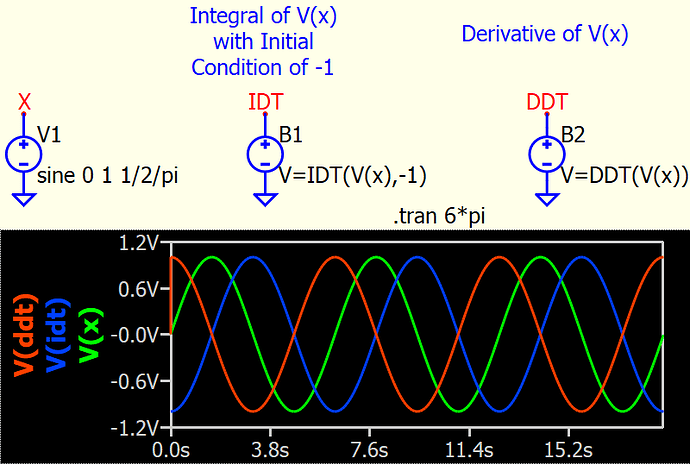

There were a number of requests for the ability to integrate and differentiate in the simulation with the normal Verilog-A functions IDT() and DDT().

I never liked how I did it in prior art – that IDT() and DDT() only reported the activity from previous timesteps so they were always off by one timestep.

The implementation in QSPICE includes the solution of the current timestep in the integration and differentiation so it should finally be correct.

This illustrates the behavior:

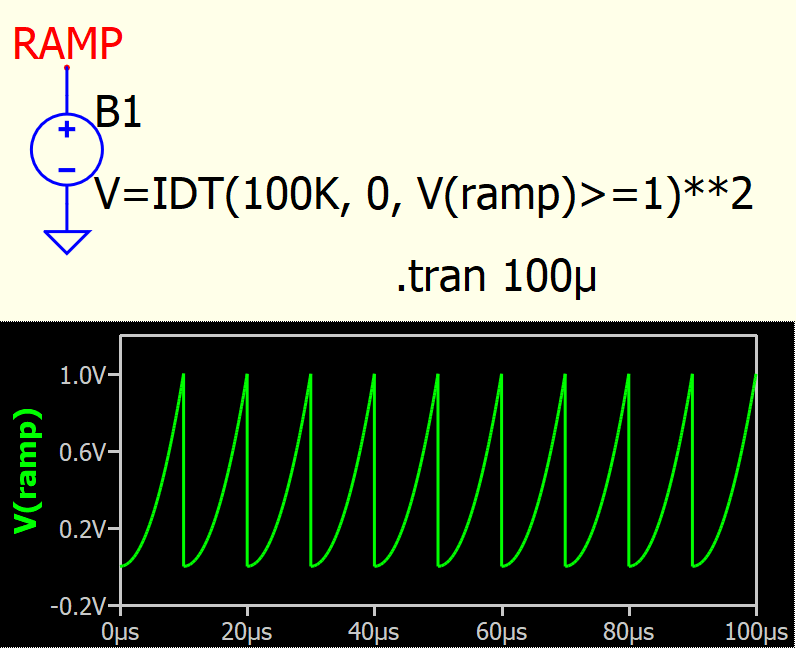

And here’s an example that shows how to make a precise 100kHz clock that can double as a quadratic slope compensation function of clocked-flop current mode controller: