Any chance you misunderstand the purpose of this test circuit or the equation? Possibly you also want through this application note : toshiba.semicon-storage.com/info/application_note_en_20200306_AKX00083.pdf?did=68907

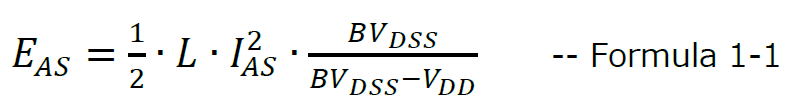

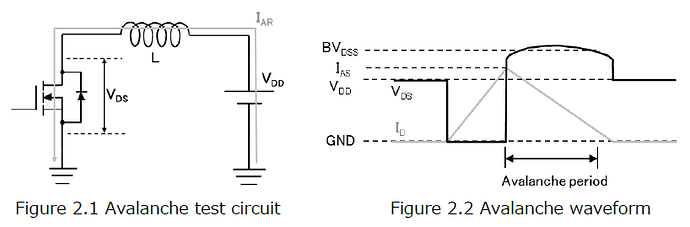

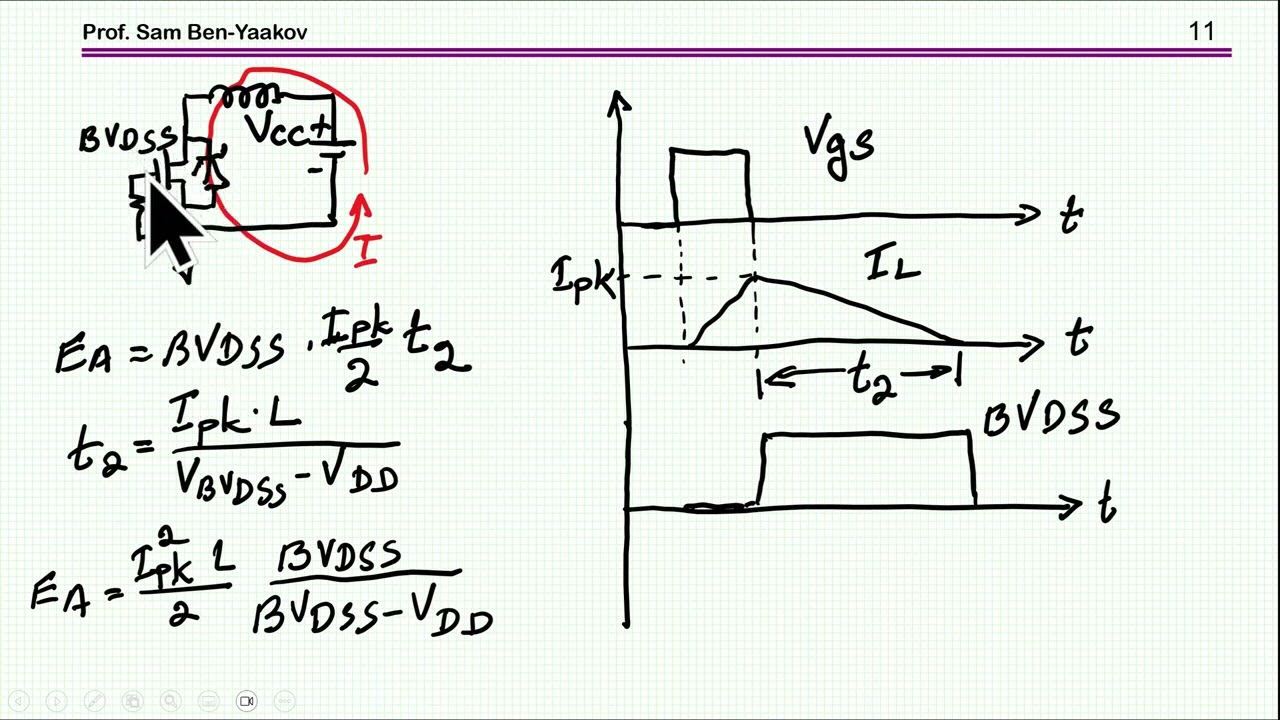

EAS is not a constant; it represents the amount of avalanche energy applied to the FET through this test setup in an ideal scenario. The manufacturer specifies the EAS and IAS values that can run into this test condition (with L, VDD, and temperature specified) without damage the FET. The values of VDD and L can control how much energy is involved during avalanche. The gate can control at what IAS value the FET turns off to begin stressing it. They are control parameters in stressing how much energy into FET during avalanche.

Prof. Sam Ben-Yaakov has a youtube video talked about avalanche