This deadtime circuit is @marcos.uniovi design. The best answer may come from Prof. Alonso.

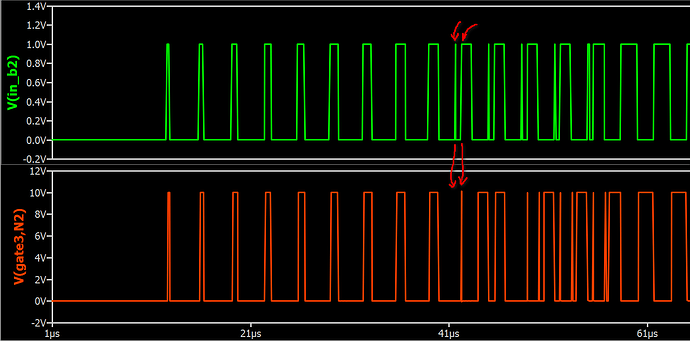

From the waveform, what you can observe is that, you have input pulse with pulse width less than deadtime. This will mess the toggle sequence in this circuit with D flip-flop and therefore, you may get an output opposite to input over time.

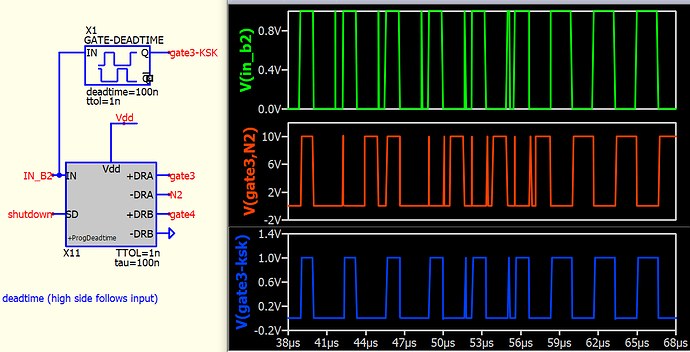

I have another deadtime logic that don’t need a flip-flop, you can check if can handle this situation. But it is logic output, and you have to add E-source to buffer the logic output to drive the FET.

Gate-DeadTime.qsym (1.8 KB)