Hello,

This is my first post, so if the information which I’m supplying is not sufficient, please let me know.

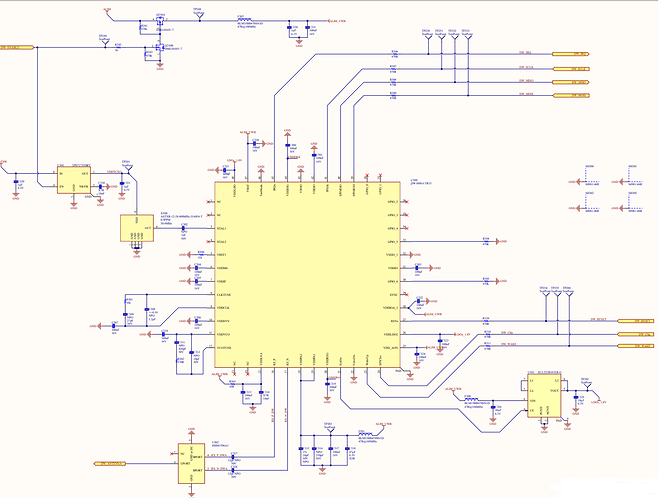

Currently I’m working a custom implementation of the DW1000 in a more complex board but I ran into some trouble.

For the custom design of the UWB part in my board, I followed a lot of the design guides. The external clock of the DW1000 is supplied by an external clock generator. I use a Taoglas antenna (Taoglas UWC .20).

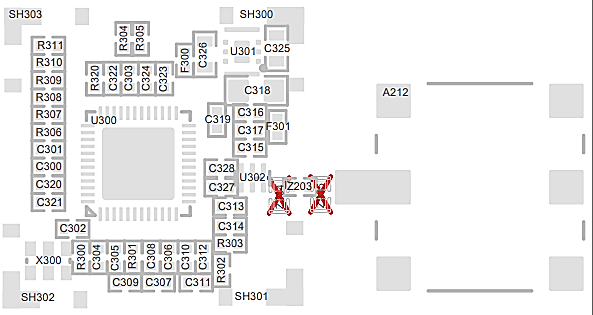

I am sorry I don’t have the PCB Layout on hand but I have the PCB Factory to give you a quick view of the implementation.

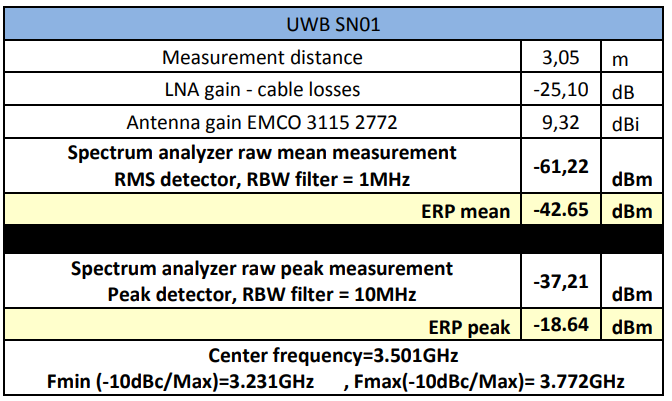

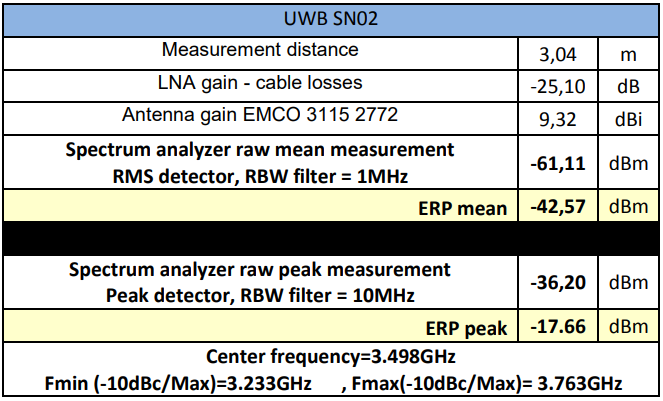

I did EMC tests in a certified lab to measure UWB ERP and Frequencies on 3 UWB beacons:

Test Procedure:

UWB ERP and Frequencies measurement are performed with a horn antenna connected to a spectrum analyser. A low noise amplifier has been used to improve the beacon signal detection. Beacon and measurement antenna are placed at a distance of ≈3m and a height of 2.2m from floor. The height has been chosen to avoid the floor influence. Front face of the beacon has been oriented toward the receive antenna. We measured the receive level with the RMS detector and a bandwidth filter of 1MHz for max mean power measurement then we used the peak detector with a bandwidth filter of 10MHz to perform the max peak power measurement. We haven’t a 50MHz bandwidth filter measurement on our receiver, so we used a 10MHz filter taking it in account in the specification (see ETSI EN 302 065-2 V2.1.1): -14dBm/10MHz instead of 0dBm/50MHz. To determine the ERP we used the Friiz equation. Beacons works in npminal mode (with recommended UWB configuration).

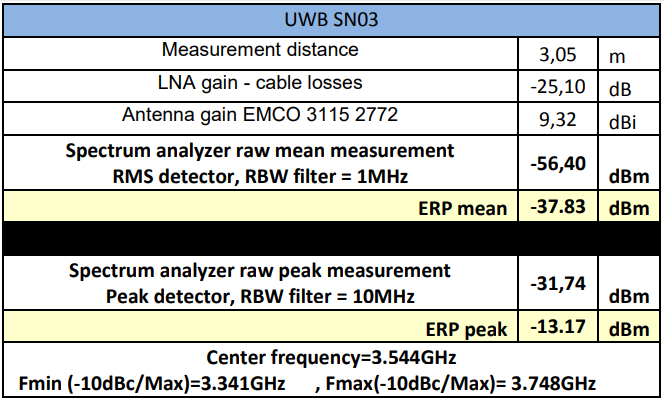

Results:

Specification:

UWB SN01: uwbTxPower=15

UWB SN02: uwbTxPower=31

UWB SN03: uwbTxPower=15

Maximum mean power (EIRP) = -41.3dBm/MHz

Maximum peak power (EIRP) = -0dBm/50MHz, measured with 10MHz filter=-14dBm/10MHz

As you can see, SN01 and SN02 are close to the specification even if SN02 is set at max uwbTxPower. SN03 is higher than the specification meanly on mean measurement even if it is set as default uwbTxPower.

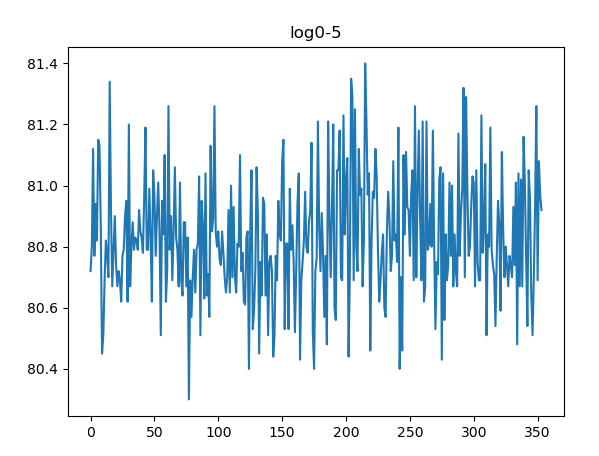

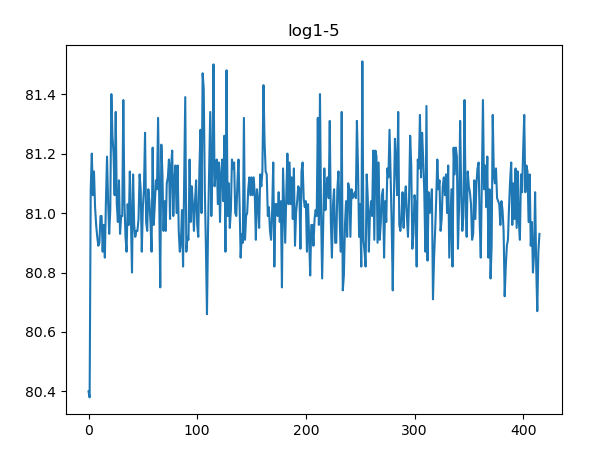

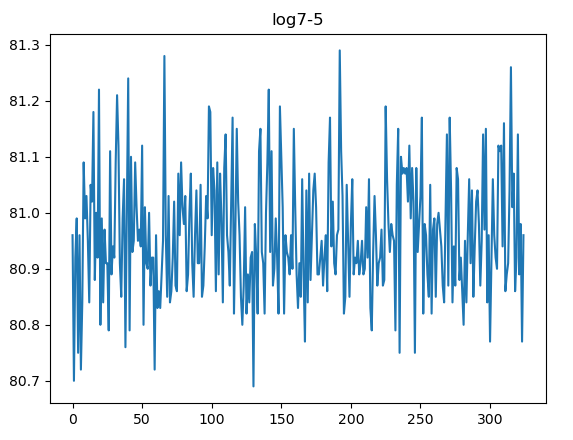

I also did a test by using a beacon as reference receptor to test the same beacons with DW1000 RXlevel value with beacon at 5.5 meters one to other and absorbent foam in open field, all three beacons has almost the same results (RXLevel by time):

In this case, all beacon seems to has same emission level and this is pretty odd, I still prefer to take the EMC lab test as right results. Do you have any clue why I have those weird behavior mostly why when I set the uwbTxPower at max on the beacon 3, the transmission power doesn’t seem to increase?