Hi Jose, here are a couple sequences I’m trying (not simultaneously):

// sample AIO10 (differential) and AIO6 (single-ended)

pac5xxx_dtse_seq_config(0, ADC0, EMUX_AIO10, 0, 0);

pac5xxx_dtse_seq_config(1, ADC0, EMUX_AIO10, 0, 0);

pac5xxx_dtse_seq_config(2, ADC0, EMUX_AB1, ADC_IRQ0_EN, 0);

pac5xxx_dtse_seq_config(3, ADC0, EMUX_AB1, 0, 1);

// alternate configuration

// sample AIO6, AIO7, and AIO8 (all single-ended)

pac5xxx_dtse_seq_config(0, ADC0, EMUX_AB1, 0, 0);

pac5xxx_dtse_seq_config(1, ADC0, EMUX_AB1, 0, 0);

pac5xxx_dtse_seq_config(2, ADC0, EMUX_AB2, 0, 0);

pac5xxx_dtse_seq_config(3, ADC0, EMUX_AB2, 0, 0);

pac5xxx_dtse_seq_config(4, ADC0, EMUX_AB3, ADC_IRQ0_EN, 0);

pac5xxx_dtse_seq_config(5, ADC0, EMUX_AB3, 0, 1);

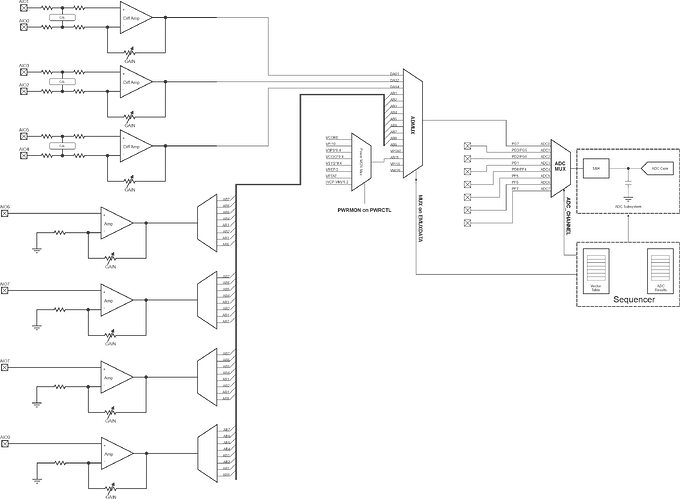

Definitely trying to replicate the example tables as much as possible. Focusing on the differential case, what I observe is that the samples from AIO6/AB1 are converted and end up in DTSERES3 and DTSERES0. Is this how the DTSE works and the wrap-around should be expected?

I also notice that the DTSERES3 result “drops out” to ~0V whereas the DTSERES0 result is more consistent. For reference, I’m sampling constant voltages right now.

Another question related to the example sequence table you provided: I understood that ADC0 was the only channel available for conversions being routed from the CAFE, is this correct? Are the conversions on ADC6 required?

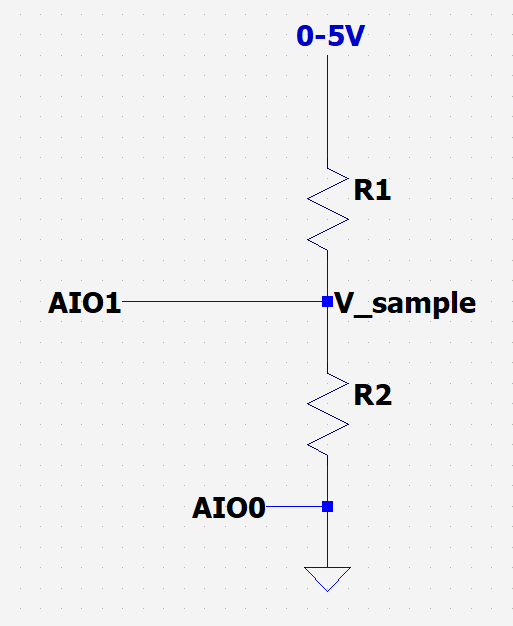

This may be better for a separate thread, but I notice too that AIO10 and AIO7/8 are not behaving like high-impedance inputs, and I get a lot of voltage drop when these pins are connected.